2007

# 2<sup>nd</sup> International Conference on Memory Technology and Design

May 7-10 2007 Giens, France

# **Proceedings**

Technical Co-Sponsor:

The Institute of Electrical and Electronics Engineers, Inc

**IEEE Electron Device Society**

# **2<sup>nd</sup> International Conference on Memory Technology and Design**

May 7 - 10 2007 Giens, France

# Proceedings

#### Organized by:

IMEC (Belgium), Catholic University of Leuven (Belgium) and L2MP (France)

#### **Technical Co-Sponsor:**

The Institute of Electrical and Electronics Engineers (IEEE), IEEE Electron Device Society

#### Sponsored by:

ARCSIS, ATMEL, LEXAR, NXP Semiconductors, STMicroelectronics, Web-Feet Research

Copyright © 2007 by ICMTD

All rights reserved

| Copyright: abstracting is permitted with credit to the source  The papers in this book reflect the authors' opinions and are published as submitted and without change. |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| The papers in this book reflect the authors' opinions and are published as submitted and without change.                                                                |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

|                                                                                                                                                                         |  |

| Additional copies may be ordered from:                                                                                                                                  |  |

| L2MP-Polytech<br>IMT Techopôle de Château Gombert                                                                                                                       |  |

| Cedex 20<br>13451 MARSEILLE                                                                                                                                             |  |

| Email: ICMTD-contact@ICMTD.com                                                                                                                                          |  |

| Website: www.ICMTD.com                                                                                                                                                  |  |

| Printed in France by the University Paul CEZANNE (Aix-Marseille III)                                                                                                    |  |

## WELCOME TO ICMTD-2007

It is our pleasure to welcome you at the 2<sup>nd</sup> International Conference on Memory Technology and Design **ICMTD-2007**, which is held from May 7<sup>th</sup>-10<sup>th</sup> 2007, again on the Peninsula of Giens at the Mediterranean coast of France.

This conference -this year being organized by the Interuniversity Microelectronics Center (IMEC), Leuven, Belgium, the Provence Materials and Microelectronics Laboratory (L2MP), Marseille, France, and the Catholic University of Leuven, Belgium- was originally created to provide an international forum for presentations and discussions on recent developments in Memory Technology and Design. All aspects of memory devices, circuits, process technologies, materials and other related research are within the scope of the conference. These three days of presentations, in oral presentations and panel discussions, provide extensive opportunities for technical information exchange. Furthermore we expect that the conference settings and social events (incl. an excursion to the Porquerolles Island) will further stimulate informal communication among participants.

49 papers have been selected for oral presentations and have been organized in 8 sessions, 6 of which being organized in parallel. Additionally, these sessions include 11 invited papers from experts in the field:

- Memory market update: shifting dynamics

- C. Hirst (Gartner Dataquest)

- Living with the DRAMification of NAND How to survive the Flash Price Wars

- A. Niebel (Webfeet Research)

- Secure memories: dream or reality?

- I. Verbauwhede (KUL)

- From memory component to memory systems

- D. Keitel-Schulz (Qimonda)

- A designer's perspective on future memory architectures for software defined radios

- P. Marchal (IMEC)

- Smart cards: technologies and products

- R. Zambrano (ST Incard)

- Phase-Change Memory Present and Future

- H.-L. Lung (Macronix)

- Current limitations of floating gate NVM and new alternatives

- A. Bergemont (Maxim Integrated Products)

- Magnetic RAM for embedded memory in SoC

- S. Ueno (Renesas)

- Copper oxide resistive switching for non-volatile memory applications

- T.-N. Fang (Spansion)

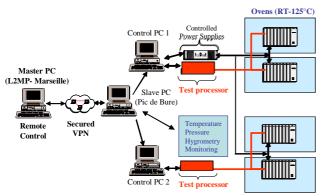

- Real-time soft-error rate testing of semiconductor memories on the european test platform ASTEP

- J.-L. Autran (L2MP)

One session deals with the exciting topic of FinFet-based Flash technology and is organized as an open workshop of the IST-FinFlash project nr. FP6-016917.

Besides these paper sessions, we also invite you to participate in 3 panel discussions

• Charge-based versus resistance-based non-volatile memory

**Moderator:** D. Wouters (*IMEC*)

**Panelists:** J. Park (Samsung), H.-L. Lung (Macronix), E. Prinz (Freescale), R. Waser (RWTH Aachen), S. Ueno (Renesas)

• SOI and new memory opportunities

**Moderator:** C. Hirst (Gartner Dataquest)

**Panelists:** D. Somasekhar (*Intel*), S. Natarajan (*Emerging Memory Technologies*), K. Itoh (*Hitachi*), P. Fazan (*Innovative Silicon*), M. Shaheen (*SOITEC*)

• Memory design in 45nm and beyond: how to survive the technology scaling

Moderator: W. Dehaene (KUL)

**Panelists:** P. Marchal (*IMEC*), D. Keitel-Schulz (*Qimonda*), I. Verbauwhede (*KUL*), D. Heslinga (*NXP Semiconductors*)

The conference also provides a limited number of posters from various memory-related European projects which can be discussed with the authors during coffee and lunch breaks.

We are confident that this conference will be an exciting event for each attendee and we would like to thank all participants for their valuable contributions to the conference.

Furthermore, we would like to express our gratitude to the Scientific/Technical committee for their review of contributed papers and to our sponsors for their financial and technical support.

Finally we would like to thank all who contributed to the organisation and implementation of the ICMTD-2007 conference.

We wish you a pleasant and fruitful conference,

Jan Van Houdt, 2007 General Chairman On behalf of the organization and steering committees

#### **ICMTD 2007 Organization:**

#### **ICMTD 2007 Communication:**

## SCIENTIFIC - TECHNICAL COMMITTEE

| Karen ATTENBOROUGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Atila ALVANDPOURLinköping University, Sweden (Linköping) |                                      |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------|--|

| Jean-Michel DAGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Karen ATTENBOROUGH                                       | NXP Semiconductors, Belgium (Leuven) |  |

| Barbara DE SALVO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Lofti BENAMMAR                                           | Atmel, Rousset (France)              |  |

| Wim DEHAENE Catholic University of Leuven, Belgium (Leuven) Pierre FAZAN Innovative Silicon Inc., Switzerland (Lauzane) Albert FAZIO Intel, USA (Santa Clara) William J. GALLAGHER IBM, USA (Yorktown Heights) Eric GERRITSEN NXP Semiconductors, France (Crolles) Yasuo INOUE Renesas, JAPAN (Tokyo) Rajiv JOSHI IBM, USA Doris KEITEL-SCHULZ Qimonda, Germany(Dresden) Zoran KRIVOKAPIC AMD, USA Pol MARCHAL IMEC, Belgium (Leuven) Pascal MASSON L2MP, France (Marseille) Pascale MAZOYER STMicroelectronics, France (Crolles) Christophe MULLER L2MP, France (Toulon) Jaekwan PARK Samsung, Korea Agostino PIROVANO STMicroelectronics, Italy(Agrate) Erwin J. PRINZ Freescale Technology, USA (Austin) Yakov ROIZIN Tower, Israel (Migdal Haemek) Kaushik ROY University of Purdue, USA (Purdue) George SAMACHISA SanDisk, USA (Santa Clara) Michiel VAN DUUREN NXP Semiconductors, Belgium Jan VAN HOUDT IMEC, Belgium (Leuven) | Jean-Michel DAGA                                         | Atmel, France (Rousset)              |  |

| Pierre FAZAN Innovative Silicon Inc., Switzerland (Lauzane) Albert FAZIO Intel, USA (Santa Clara) William J. GALLAGHER IBM, USA (Yorktown Heights) Eric GERRITSEN NXP Semiconductors, France (Crolles) Yasuo INOUE Renesas, JAPAN (Tokyo) Rajiv JOSHI IBM, USA Doris KEITEL-SCHULZ Qimonda, Germany(Dresden) Zoran KRIVOKAPIC AMD, USA Pol MARCHAL IMEC, Belgium (Leuven) Pascal MASSON L2MP, France (Marseille) Pascale MAZOYER STMicroelectronics, France (Crolles) Christophe MULLER L2MP, France (Toulon) Jaekwan PARK Samsung, Korea Agostino PIROVANO STMicroelectronics, Italy(Agrate) Erwin J. PRINZ Freescale Technology, USA (Austin) Yakov ROIZIN Tower, Israel (Migdal Haemek) Kaushik ROY University of Purdue, USA (Purdue) George SAMACHISA SanDisk, USA (Santa Clara) Michiel VAN DUUREN NXP Semiconductors, Belgium Jan VAN HOUDT IMEC, Belgium (Leuven)                                                             |                                                          |                                      |  |

| Albert FAZIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |                                      |  |

| William J. GALLAGHER  BM, USA (Yorktown Heights)  Eric GERRITSEN  NXP Semiconductors, France (Crolles)  Yasuo INOUE  Renesas, JAPAN (Tokyo)  Rajiv JOSHI  IBM, USA  Doris KEITEL-SCHULZ  Qimonda, Germany(Dresden)  Zoran KRIVOKAPIC  AMD, USA  Pol MARCHAL  IMEC, Belgium (Leuven)  Pascal MASSON  L2MP, France (Marseille)  Pascale MAZOYER  STMicroelectronics, France (Crolles)  Christophe MULLER  L2MP, France (Toulon)  Jaekwan PARK  Samsung, Korea  Agostino PIROVANO  STMicroelectronics, Italy(Agrate)  Erwin J. PRINZ  Freescale Technology, USA (Austin)  Yakov ROIZIN  Tower, Israel (Migdal Haemek)  Kaushik ROY  University of Purdue, USA (Purdue)  George SAMACHISA  SanDisk, USA (Santa Clara)  Michiel VAN DUUREN  NXP Semiconductors, Belgium  Jan VAN HOUDT  IMEC, Belgium (Leuven)                                                                                                                             |                                                          |                                      |  |

| Eric GERRITSEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Albert FAZIO                                             | Intel, USA (Santa Clara)             |  |

| Yasuo INOUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | William J. GALLAGHER                                     | IBM, USA (Yorktown Heights)          |  |

| Rajiv JOSHI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Eric GERRITSEN                                           | NXP Semiconductors, France (Crolles) |  |

| Doris KEITEL-SCHULZ. Qimonda, Germany(Dresden)  Zoran KRIVOKAPIC. AMD, USA  Pol MARCHAL. IMEC, Belgium (Leuven)  Pascal MASSON. L2MP, France (Marseille)  Pascale MAZOYER. STMicroelectronics, France (Crolles)  Christophe MULLER. L2MP, France (Toulon)  Jaekwan PARK. Samsung, Korea  Agostino PIROVANO. STMicroelectronics, Italy(Agrate)  Erwin J. PRINZ. Freescale Technology, USA (Austin)  Yakov ROIZIN. Tower, Israel (Migdal Haemek)  Kaushik ROY. University of Purdue, USA (Purdue)  George SAMACHISA. SanDisk, USA (Santa Clara)  Michiel VAN DUUREN. NXP Semiconductors, Belgium  Jan VAN HOUDT. IMEC, Belgium (Leuven)                                                                                                                                                                                                                                                                                                 | Yasuo INOUE                                              | Renesas, JAPAN (Tokyo)               |  |

| Zoran KRIVOKAPIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Rajiv JOSHI                                              | IBM, USA                             |  |

| Pol MARCHAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Doris KEITEL-SCHULZ                                      | Qimonda, Germany(Dresden)            |  |

| Pascal MASSON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |                                      |  |

| Pascale MAZOYER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pol MARCHALIMEC, Belgium (Leuven)                        |                                      |  |

| Christophe MULLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |                                      |  |

| Jaekwan PARK Samsung, Korea  Agostino PIROVANO STMicroelectronics, Italy(Agrate)  Erwin J. PRINZ Freescale Technology, USA (Austin)  Yakov ROIZIN Tower, Israel (Migdal Haemek)  Kaushik ROY University of Purdue, USA (Purdue)  George SAMACHISA SanDisk, USA (Santa Clara)  Michiel VAN DUUREN NXP Semiconductors, Belgium  Jan VAN HOUDT IMEC, Belgium (Leuven)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pascale MAZOYER                                          | STMicroelectronics, France (Crolles) |  |

| Agostino PIROVANO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |                                      |  |

| Erwin J. PRINZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Jaekwan PARK                                             | Samsung, Korea                       |  |

| Yakov ROIZIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Agostino PIROVANO                                        | STMicroelectronics, Italy(Agrate)    |  |

| Kaushik ROY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Erwin J. PRINZ                                           | Freescale Technology, USA (Austin)   |  |

| George SAMACHISASanDisk, USA (Santa Clara)  Michiel VAN DUURENNXP Semiconductors, Belgium  Jan VAN HOUDTIMEC, Belgium (Leuven)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Yakov ROIZIN                                             | Tower, Israel (Migdal Haemek)        |  |

| Michiel VAN DUURENNXP Semiconductors, Belgium  Jan VAN HOUDTIMEC, Belgium (Leuven)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Kaushik ROY                                              | University of Purdue, USA (Purdue)   |  |

| Jan VAN HOUDTIMEC, Belgium (Leuven)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | George SAMACHISASanDisk, USA (Santa Clara)               |                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Michiel VAN DUURENNXP Semiconductors, Belgium            |                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Jan VAN HOUDTIMEC, Belgium (Leuven)                      |                                      |  |

| Rainer WASERRWTH Aachen, Germany (Aachen)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Rainer WASER                                             | RWTH Aachen, Germany (Aachen)        |  |

| Josef WILLERQimonda, Germany (Aachen)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Josef WILLER                                             | Qimonda, Germany (Aachen)            |  |

| Dirk WOUTERSIMEC, Belgium (Leuven)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Dirk WOUTERS                                             | IMEC, Belgium (Leuven)               |  |

## ICMTD STEERING - COMMITTEE

| Atila ALVANDPOUR | Linköping University, Sweden (Linköping) |

|------------------|------------------------------------------|

| Jean-Michel DAGA | Atmel, France (Rousset)                  |

| Eric GERRITSEN   | NXP Semiconductors, France (Crolles)     |

| Pascal MASSON    | L2MP, France (Marseille)                 |

| Pascale MAZOYER  | STMicroelectronics, France (Crolles)     |

| Jaekwan PARK     | Samsung, Korea                           |

| Erwin J. PRINZ   | Freescale Technology, USA (Austin)       |

| Jan VAN HOUDT    | IMEC, Belgium (Leuven)                   |

## TABLE OF CONTENT

|            | EVENING LECTURE: Memory market update: shifting dynamics                                                                                                                                                                                                                                                                                               | 5          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|            | C. Hirst (Gartner Dataquest)  PANEL DISCUSSION: Charge-based versus resistance-based non-volatile memory  Moderator: D. Wouters (IMEC)                                                                                                                                                                                                                 | 7          |

|            | Panelists: H.L. Lung (Macronix), J. Park (Samsung), E. Prinz (Freescale), R. Waser (RWTH Aachen),                                                                                                                                                                                                                                                      |            |

|            | S. Ueno (Renesas), R. Waser (RWTH Aechen)  PANEL DISCUSSION: SOI and new memory opportunities                                                                                                                                                                                                                                                          | 9          |

|            | Moderator: C. Hirst (Gartner Dataquest) Panelists: P. Fazan (Innovative Silicon), K. Itoh (Hitachi), S. Natarajan (Emerging Memory Technologies),                                                                                                                                                                                                      |            |

|            | M. Shaheen (SOITEC), D. Somasekhar (Intel)                                                                                                                                                                                                                                                                                                             |            |

|            | PANEL DISCUSSION: Memory design in 45nm and beyond: how to survive the technology scaling?                                                                                                                                                                                                                                                             | 11         |

|            | Moderator: W. Dehaene (KUL) Panelists: D. Heslinga (NXP Semiconductors), D. Keitel-Schulz (Qimonda), P. Marchal (IMEC), I. Verbauwhede (KUL)                                                                                                                                                                                                           |            |

|            | LIST OF AUTHORS                                                                                                                                                                                                                                                                                                                                        | 255        |

|            | NOTES                                                                                                                                                                                                                                                                                                                                                  | 259        |

| SESS       | SION A : Invited Talks                                                                                                                                                                                                                                                                                                                                 |            |

| A-1        | Living with the DRAMification of NAND - How to survive the Flash Price Wars                                                                                                                                                                                                                                                                            | 15         |

| A-2        | A. Niebel (Webfeet Research) Secure memories: dream or reality?                                                                                                                                                                                                                                                                                        | 17         |

| A-2        | I. Verbauwhede (KUL)                                                                                                                                                                                                                                                                                                                                   | 1 /        |

| A-3        | From memory component to memory systems  D. Keitel-Schulz (Qimonda)                                                                                                                                                                                                                                                                                    | 21         |

| A-4        | A designer's perspective on future memory architectures for software defined radios  P. Marchal ( <i>IMEC</i> ), B. Bougard ( <i>IMEC</i> ), A. Papanikolaou ( <i>IMEC</i> ), M. Miranda ( <i>IMEC</i> ),  F. Catthoor ( <i>IMEC-ESAT</i> ), W. Dehaene ( <i>ESAT</i> )                                                                                | 25         |

| A-5        | Smart cards: technologies and products                                                                                                                                                                                                                                                                                                                 | 29         |

|            | R. Zambrano (ST Incard), E. Toscano (ST Incard), A. Conte (STMicroelectronics)                                                                                                                                                                                                                                                                         |            |

| SESS       | SION B : Phase Change Memory                                                                                                                                                                                                                                                                                                                           |            |

| B-1        | Invited: "Phase-Change Memory – Present and Future" HL. Lung (Macronix), M. Breitwisch (IBM), T. Happ (Qimonda), C. Lam (Qimonda)                                                                                                                                                                                                                      | 35         |

| B-2        | Heater electrode engineering and analysis of series resistance in phase change memory                                                                                                                                                                                                                                                                  | 39         |

| D 2        | C.W. Jeong, D.H. Kang, D.W. Ha, Y.J. Song, J.H. Oh, J.H. Kong, J.H. Yoo, J.H. Park, K.C. Ryoo, D.W. Lim, S.S. Park, J.I. Kim, Y.T. Oh, J.S. Kim, J.M. Shin, J. Park, Y. Fai, Y.T. Kim, G.H. Koh,                                                                                                                                                       | 37         |

| B-3        | G.T. Jeong, H.S. Jeong, K. Kim (Samsung)  Effects of the crystallization statistics on programming distributions in phase-change                                                                                                                                                                                                                       | 43         |

|            | memory arrays  D. Mantegazza (Politecnico di Milano), D. Ielmini (Politecnico di Milano), A. Pirovano (STMicroelectronics), A.L. Lacaita (Politecnico di Milano), E. Varesi (STMicroelectronics), F. Pellizzer (STMicroelectronics), R. Bez (STMicroelectronics)                                                                                       |            |

| <b>B-4</b> | A low power PRAM using a power-dependent data inversion scheme                                                                                                                                                                                                                                                                                         | 47         |

|            | BD. Yang (Chungbuk National University), J.E. Lee (Chungbuk National University), J.S. Kim (Chungbuk National University), J.K. Yun (Chungbuk National University), S.Y. Lee (ETRI), Y.S. Park (ETRI), S.M. Yoon (ETRI), B.G. Yu (ETRI)                                                                                                                |            |

| <b>B-5</b> | Threshold switching in doped SbTe phase change line cells                                                                                                                                                                                                                                                                                              | 51         |

|            | F. J. Jedema (NXP Semiconductors), J. van der Wagt (NXP Semiconductors), M. A.A. in 't Zandt (NXP Semiconductors), R. A.M. Wolters (NXP Semiconductors), B. W.S.M.M. Ketelaars (Philips Research), R. Delhougne (NXP Semiconductors), D. Tio Castro (NXP Semiconductors), D. J. Gravesteijn (NXP Semiconductors), V. Attenhorgych (NXP Semiconductors) |            |

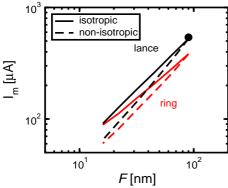

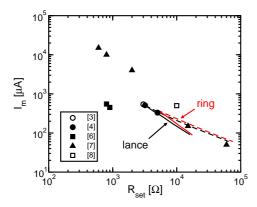

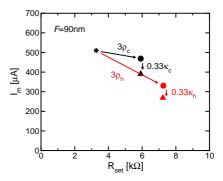

| B-6        | Semiconductors), K. Attenborough (NXP Semiconductors)  Geometry and material optimization for programming current scaling in phase-change                                                                                                                                                                                                              | 55         |

| <b>D</b> 0 | memory                                                                                                                                                                                                                                                                                                                                                 | 33         |

| n -        | U. Russo, A. Redaelli, D. Ielmini, A.L. Lacaita (Politecnico di Milano)                                                                                                                                                                                                                                                                                | <b>=</b> 0 |

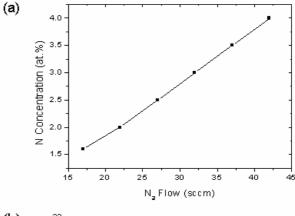

| B-7        | Composition variations of nitrogen doped Ge-Sb-Te thin films and their read/write properties for phase change memories                                                                                                                                                                                                                                 | 59         |

|            | H Lim D Kim G Oh S I Kang N H Lim Y Ha I Bae I Oh I Park H D Lee I T Moon (Samsung)                                                                                                                                                                                                                                                                    |            |

1

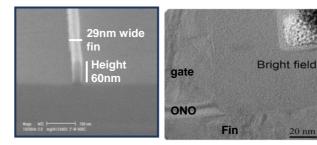

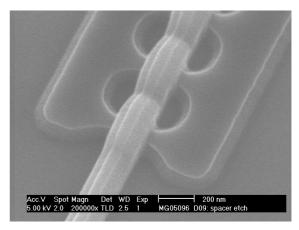

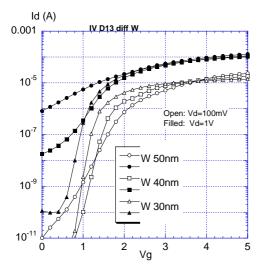

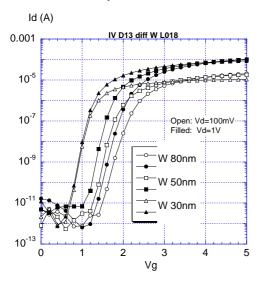

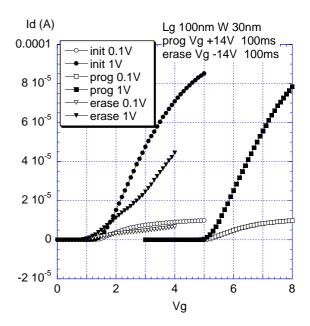

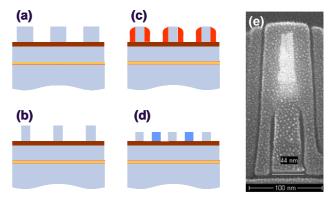

| C-1 | FinFET SONOS non-volatile memory arrays D. S. Golubović, N. Akil, M. van Duuren, A. H. Miranda, R. van Schaijk (NXP Semiconductors)                                                                                                                                                                                                                                                                                                                                                                | 65 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| C-2 | Corner enhancement of FNT program/erase operations in nitride storage FinFLASH devices  L. Breuil, M. Rosmeulen, J. Loo, A. Furnémont, L. Haspeslagh, J. Van Houdt ( <i>IMEC</i> )                                                                                                                                                                                                                                                                                                                 | 69 |

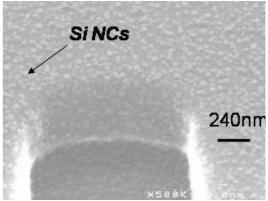

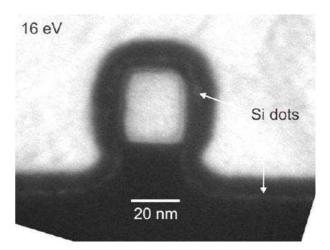

| C-3 | Program / erase characteristics of ultra-scaled Si Nanocrystal FINFLASH memories S. Lombardo (CNR-IMM), C. Gerardi (STMicroelectronics), D. Corso (CNR-IMM), G. Cina (STMicroelectronics), E. Tripiciano (CNR-IMM), V. Ancarani (STMicroelectronics), C. Buongiorno (CNR-IMM), E. Rimini (CNR-IMM), M. Melanotte (STMicroelectronics)                                                                                                                                                              | 73 |

| C-4 | Physical insights on design of SONOS FinFETs programmed with channel tunneling F. Nardi, G. Iannaccone ( <i>Università di Pisa</i> )                                                                                                                                                                                                                                                                                                                                                               | 77 |

| C-5 | Study of programming characteristics of 4-bit SONOS flash memory using 3-dimensional transient simulation J.G. Yun, Y. Kim, I. H. Park, S. Cho, J. H. Lee, G. S. Lee, D.H. Kim, D. H. Lee, S.H. Park, J.D. Lee, B.G. Park (ISRC)                                                                                                                                                                                                                                                                   | 81 |

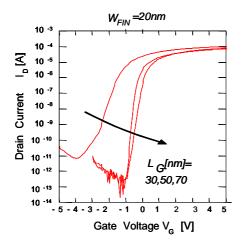

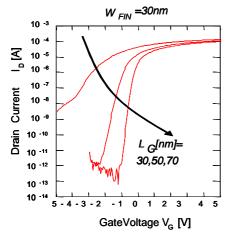

| C-6 | Investigation of the impacts of channel length, fin width on Si-NC SOI-FinFlash memory characteristics  C. Jahan ( <i>Leti</i> ), J. Razafindramora ( <i>Leti</i> ), L. Perniola ( <i>Leti</i> ), M. Gély ( <i>Leti</i> ), C. Vizioz ( <i>Leti</i> ), A. Toffoli ( <i>Leti</i> ), F. Allain ( <i>Leti</i> ), S. Lombardo ( <i>CNR-IMM</i> ), C. Bongiorno ( <i>CNR-IMM</i> ), G. Reimbold ( <i>Leti</i> ), F.Boulanger ( <i>Leti</i> ), B. De Salvo ( <i>Leti</i> ), S. Deleonibus ( <i>Leti</i> ) | 85 |

| D-1 | Invited: "Current limitations of floating gate NVM and new alternatives"  A. Bergemont (Maxim integrated products)                                                                                                                                                                                                        | 91  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| D-2 | <b>The Moving Bits: Generation and Annealing</b> S. Mouhoubi ( <i>L2MP</i> ), T. Yao ( <i>AMI-Semiconductor</i> ), A. Lowe ( <i>AMI-Semiconductor</i> ), P. Gassot ( <i>AMI-Semiconductor</i> ), F. Lalande ( <i>L2MP</i> )                                                                                               | 95  |

| D-3 | Improvement of retention and Vth window in Flash memory device through optimization of floating gate doping C. Shen, J. Pu, M.F. Li, B. J. Cho (National University of Singapore)                                                                                                                                         | 99  |

| D-4 | A single-poly NVM based on a CMOS inverter with a common floating gate Y. Roizin, A. Fenigstein, V. Kairys, Z. Kuritsky, A. Lahav (Tower)                                                                                                                                                                                 | 103 |

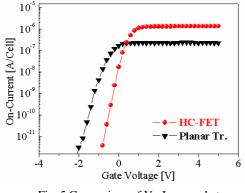

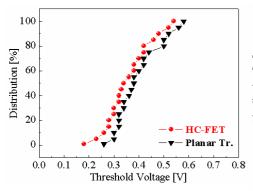

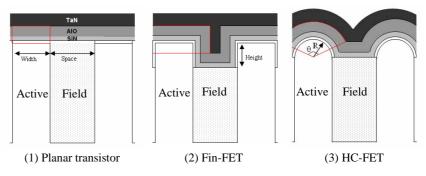

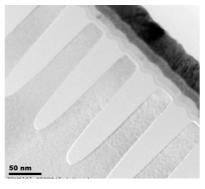

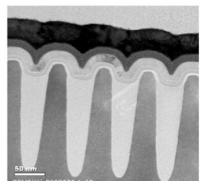

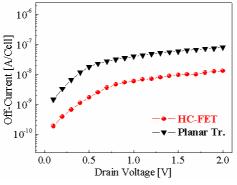

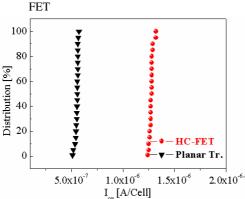

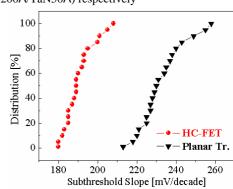

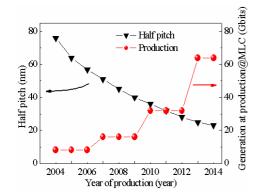

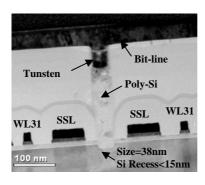

| D-5 | Introduction of HC (Hemi Cylindrical)-FET for development of NAND CTF (Charge Trap Flash) cell with 76nm pitch technology S. Park, B. Hwang, H. Park, Y. Lee, S. Kwon, K. Lee, M. Kim, J. Kim, D. Kwak, Y. Yim, J. Park, K. Kim, K. Kim (Samsung) <sup>2</sup>                                                            | 107 |

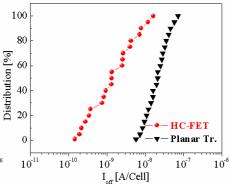

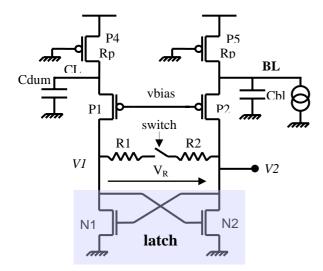

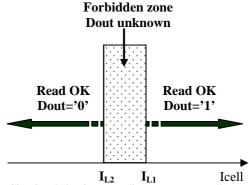

| D-6 | A self-synchronized, 1V operation read circuitry for high speed advanced embedded flash memories  J. Fort, J.M. Daga (Atmel)                                                                                                                                                                                              | 109 |

| D-7 | A low voltage, low power, highly reliable, multi-purpose, cost-competitive embedded non-volatile memory in 90nm node G. Tao (NXP Semiconductors), E. van der Vegt (NXP Semiconductors), J.P. Carrère (STMicroelectronics), F. Larman (NXP Semiconductors), D. Boter (NXP Semiconductors), D. Dormans (NXP Semiconductors) | 113 |

| D-8 | Data retention reliability of P+ Poly floating gate memories in logic CMOS processes Y. Ma, R. Deng, B. Wang, A. Horch, R. Paulsen (Impinj Inc)                                                                                                                                                                           | 117 |

## SESSION E: RRAM & DRAM

| E-1   | Invited: "Magnetic RAM for embedded memory in SoC"  S. Ueno (Renesas Technology Corp.), K. Kuroiwa (Mitsubishi Electric Corp.), T. Tsuji (Renesas Technology Corp.), H. Tanizaki (Renesas Design Corp.), M. Shimizu (Renesas Technology Corp.), Y. Inoue (Renesas Technology Corp.)                                                                                                                                                                                      | 123 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

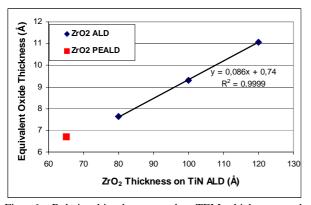

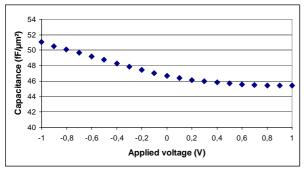

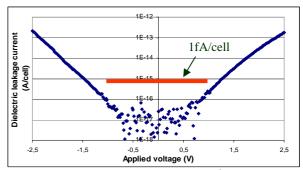

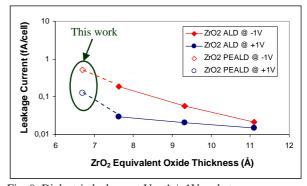

| E-2   | Performances of a ZrO <sub>2</sub> PEALD Dielectric for 45nm Embedded DRAM 3D MIM (Metal-Insulator-Metal) Stacked Capacitors  A. Berthelot (NXP Semiconductors), C. Caillat (STMicroelectronics), H. Del-Puppo (Freescale), B. Icard (Leti), E. Deloffre (STMicroelectronics), N. Emonet (STMicroelectronics), M. Gros-Jean (STMicroelectronics), S. Barnola (Leti), C. Soonekindt (NXP Semiconductors), R. Pantel (STMicroelectronics), F. Lalanne (STMicroelectronics) | 127 |

| E-3   | Conductance switching behaviour of a phenol substituted bithiophene memory device M. Caironi, D. Natali, M. Sampietro, C. Bertarelli, A. Bianco, E. Canesi, G. Zerbi ( <i>Politecnico di Milano</i> )                                                                                                                                                                                                                                                                    | 131 |

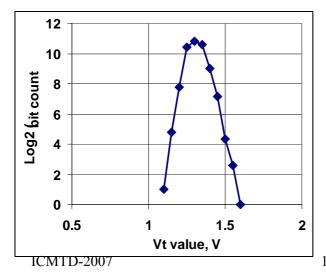

| E-4   | Improved CuTCNQ resistive non-volatile memories and a statistical study on their threshold voltage J. Billen, R. Müller, J. Genoe, P. Heremans (IMEC)                                                                                                                                                                                                                                                                                                                    | 135 |

| E-5   | The Influence of Different Electrode Materials on Resistive Switching in Cu:7,7,8,8-Tetracyanoquinodimethane Thin Films T. Kever, U. Böttger, R. Waser (RWTH Aachen University)                                                                                                                                                                                                                                                                                          | 139 |

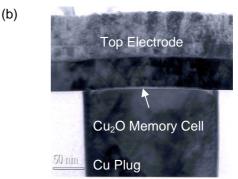

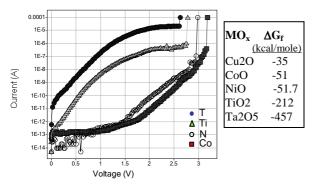

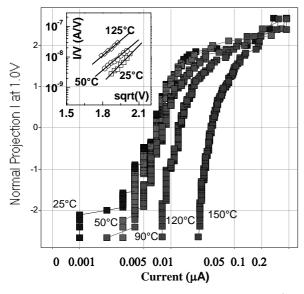

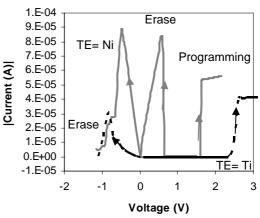

| E-6   | Invited: "Copper Oxide Resistive Switching for Non-Volatile Memory Applications" T.N. Fang (Spansion)                                                                                                                                                                                                                                                                                                                                                                    | 143 |

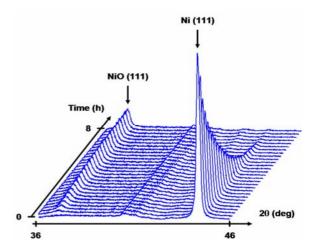

| E-7   | Resistive switching and microstructure of NiO binary oxide films developed for OxRRAM non-volatile memories  L. Courtade ( <i>L2MP</i> ), C. Turquat ( <i>L2MP</i> ), C. Muller ( <i>L2MP</i> ), D. Goguenheim ( <i>L2MP</i> ),  J.G. Lisoni ( <i>IMEC</i> ), L. Goux ( <i>IMEC</i> ), D.J. Wouters ( <i>IMEC</i> )                                                                                                                                                      | 147 |

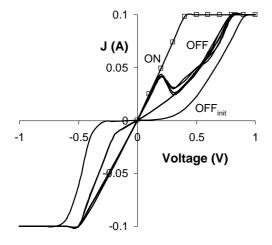

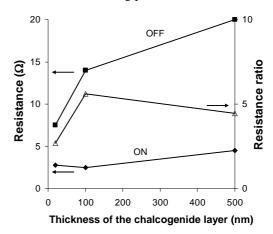

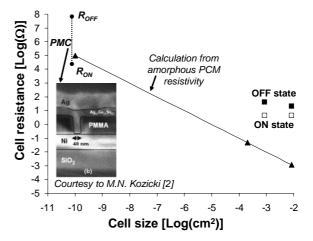

| E-8   | Switching between two high-resistive states in Cu/chalcogenide/W structures for application in non-volatile memories  L. Goux ( <i>IMEC</i> ), J. G. Lisoni ( <i>IMEC</i> ), T. Gille ( <i>IMEC</i> ), K. De Meyer ( <i>IMEC</i> ), K. Attenborough (NXP Semiconductors), D. J. Wouters ( <i>IMEC</i> )                                                                                                                                                                  | 151 |

| E-9   | 1TBulk eDRAM a reliable concept for nanometre scale high density and low power applications  S. Puget (NXP Semiconductors), G. Bossu (STMicroelectronics), C. Guerin (STMicroelectronics), R. Ranica (STMicroelectronics), A. Villaret (STMicroelectronics), P. Masson (L2MP), J-M. Portal (L2MP), R. Bouchakour (L2MP), P. Mazoyer (STMicroelectronics), V. Huard (NXP Semiconductors), T. Skotnicki (STMicroelectronics)                                               | 155 |

| SESSI | ON F : SRAM & Process Variability                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

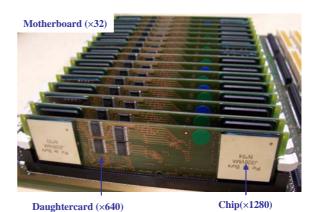

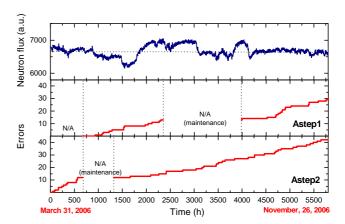

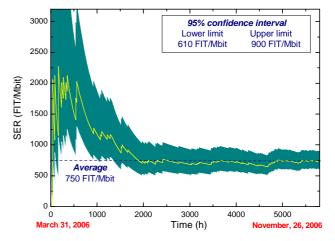

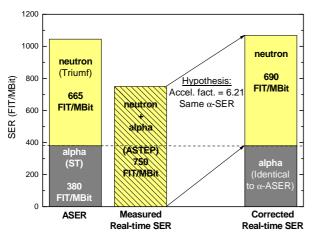

| F-1   | Invited: "Real-time soft-error rate testing of semiconductor memories on the european test platform ASTEP"  JL. Autran ( <i>L2MP-IUF</i> ), P. Roche ( <i>STMicroelectronics</i> ), G. Gasiot ( <i>STMicroelectronics</i> ), D. Munteanu ( <i>L2MP</i> ), T. Parrassin ( <i>STMicroelectronics</i> ), J. Borel ( <i>JB R&amp;D</i> ), J.P. Schoellkopf ( <i>STMicroelectronics</i> )                                                                                     | 161 |

| F-2   | Low voltage SRAM with noble cell bias technique to increase static noise margin Y. Chung, S.H. Song, Y.J. Eom, S.W. Shim (Kyungpook National University)                                                                                                                                                                                                                                                                                                                 | 165 |

| F-3   | A Noise-Margin Monitor for SRAMs P. Geens, W. Dehaene (Katholieke Universiteit Leuven)                                                                                                                                                                                                                                                                                                                                                                                   | 169 |

| F-4   | A variability tolerant embedded SRAM offering runtime selectable energy/delay figures H. Wang ( <i>IMEC</i> ), M. Miranda ( <i>IMEC</i> ), P. Geens ( <i>KUL</i> ), W. Dehaene ( <i>KUL</i> ), F. Catthoor ( <i>IMEC</i> )                                                                                                                                                                                                                                               | 173 |

| F-5   | Protection of embedded memory systems - a comprehensive solution  R. Mariani (Yogitech SpA), F. Colucci (Yogitech SpA), P. Fuhrmann (Philips Research Laboratories)                                                                                                                                                                                                                                                                                                      | 177 |

| F-6   | Bit cell leakage-aware SRAM sense amplifier activation schemes  T. Song (Georgia Institute), K. Lim (Georgia Institute), G. Kim (Samsung), I. Son (Samsung),  J. Laskar (Georgia Institute)                                                                                                                                                                                                                                                                              | 181 |

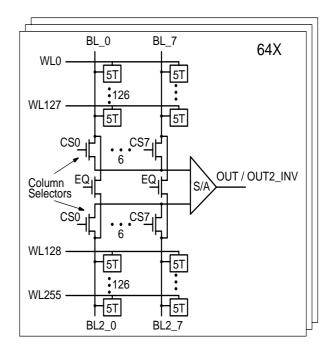

| F-7   | A 128Kb 5T SRAM in 0.18µm CMOS S. Andersson (Linkoping University), I. Carlson (Linkoping University), S. Natarajan (Emerging Memory Technologies Inc/Linkoping University), A. Alvandpour (Linkoping University)                                                                                                                                                                                                                                                        | 185 |

| ומפתומ | told G. Charge Trapping                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| G-1    | Sub-lithographical Shrink of Twin Flash <sup>TM</sup> Memory Cells to the 32 nm Technology Node M.F. Beug ( <i>Qimonda</i> ), R. Knoefler ( <i>Qimonda</i> ), C. Ludwig ( <i>Qimonda</i> ), R. Hagenbeck ( <i>Qimonda</i> ), T. Müller ( <i>Qimonda</i> ), S. Riedel ( <i>Qimonda</i> ), M. Isler ( <i>Qimonda</i> ), M. Strassburg ( <i>Qimonda</i> ), T. Höhr ( <i>Qimonda</i> ), T. Mikolajick ( <i>TU Bergakademie Freiberg</i> ), K.H. Küsters ( <i>Qimonda</i> ) | 191 |

| G-2    | An embedded spacer-trapping memory in the CMOS technology E. Pikhay (Tower), Y. Roizin (Tower), A. Fenigstein (Tower), A. Heiman (Tower), E. Aloni (Tower), G. Rosenman (Tel Aviv University)                                                                                                                                                                                                                                                                          | 195 |

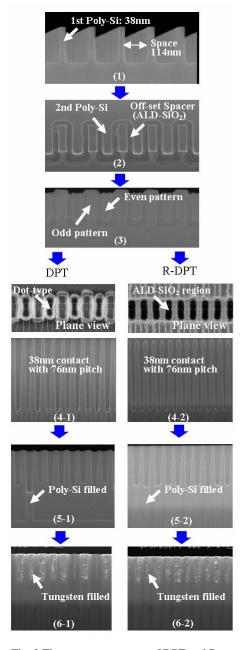

| G-3    | Comparison of DPT (Double Patterning Technology) vs. R (Reversal)-DPT using Off-set spacer for Bit-line contacts of 76nm pitch on NAND Flash cell J.H. Park, B. Hwang, J. Shim, K. Lee, S. Kwon, S.Y. Park, D. Kwak, J. Park, K. Kim, K. Kim (Samsung)                                                                                                                                                                                                                 | 199 |

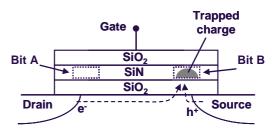

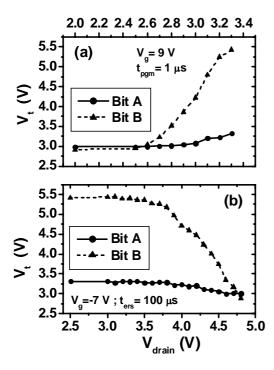

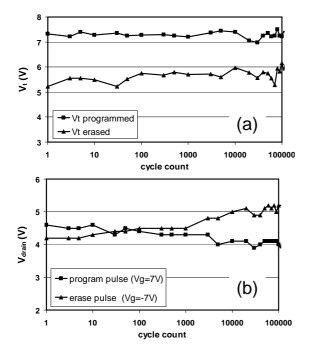

| G-4    | Depletion 2-Transistor-SONOS Flash memories with zero gate voltage read out N. Akil, M. van Duuren, D. Dormans, D. Boter, A. H. Miranda, D. Golubović, R. van Schaijk, M. Slotboom (NXP Semiconductors)                                                                                                                                                                                                                                                                | 201 |

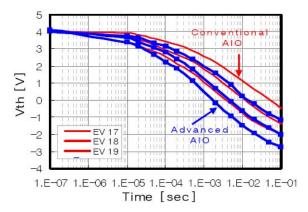

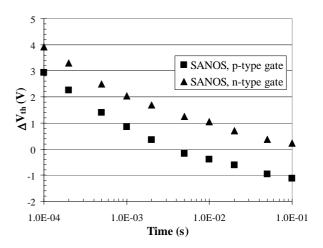

| G-5    | Physical understanding and modeling of SANOS retention in programmed state A. Furnémont, M. Rosmeulen, A. Cacciato, L. Breuil, J. Van Houdt, K. De Meyer, H. Maes (IMEC)                                                                                                                                                                                                                                                                                               | 205 |

| G-6    | The 40 nm TANOS (Si – Oxide - SiN – Al2O3 – TaN) Cell Technologies for 32Gb NAND Flash Memory  B. Choi, Y. Park, J. Choi, C. Kang, C. Lee, Y. Shin, J. Kim, S. Jeon, J. Sel, J. Park, J. Sim, Y. Kim, S.k. Hwang (Samsung)                                                                                                                                                                                                                                             | 209 |

| G-7    | SONOS-type memory structures using thin silicon nitride films modified by low-energy Si+implantation  P. Dimitrakis (NCRS), V. Ioannou-Sougleridis (NCRS), V. Em.Vamvakas (NCRS), P. Normand (NCRS), C. Bonafos (CEMES-CNRS), S. Schamm (CEMES-CNRS), N. Cherkashin (CEMES-CNRS), G. Ben Assayag (CEMES-CNRS), M. Perego (MDM CNR-INFM), M. Fanciulli (MDM CNR-INFM)                                                                                                   | 213 |

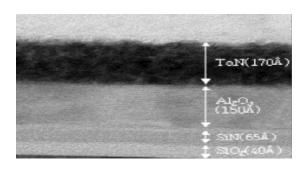

| G-8    | Effect of Al <sub>2</sub> O <sub>3</sub> morphology on the erase saturation performance in SANOS-type memory cells  A. Cacciato, A. Furnémont, L. Breuil, J. De Vos, L. Haspeslagh, J. Van Houdt ( <i>IMEC</i> )                                                                                                                                                                                                                                                       | 217 |

| SESSI  | ION H : High-κFlash & Nano-crystals                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| H-1    | A Systematic Study of High-K Interpoly Dielectric Structures for Floating Gate Flash Memory Devices L. Zhang, W. He, D. S.H. Chan, B. J. Cho (National University of Singapore)                                                                                                                                                                                                                                                                                        | 223 |

| H-2    | Use of Al <sub>2</sub> O <sub>3</sub> as Inter-Poly Dielectric in a Production proven 130nm embedded Flash Technology R. Kakoschke, L. Pescini, J.R. Power, K. van der Zanden, EO. Andersen, Y. Gong, R. Allinger (Infineon)                                                                                                                                                                                                                                           | 225 |

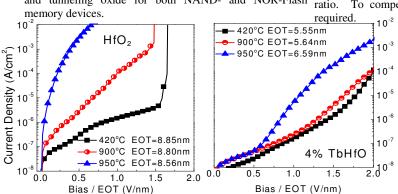

| Н-3    | Investigation of aggressively scaled HfAlO <sub>x</sub> -based interpoly dielectric stacks for sub-45 nm nonvolatile memory technologies  B. Govoreanu (IMEC), D. Wellekens (IMEC), L. Haspeslagh (IMEC), D.P. Brunco (Intel), J. De Vos (IMEC), D. Ruiz Aguado (IMEC), P. Blomme (IMEC), K. van der Zanden (Infineon), J. Van Houdt (IMEC)                                                                                                                            | 231 |

| H-4    | High-Quality Aluminum-Oxide Tunnel Barriers for Scalable, Floating-Gate Random-Access Memories (FGRAM) X. Liu, V. Patel, Z. Tan, K. K. Likharev, J. E. Lukens (Stony Brook University)                                                                                                                                                                                                                                                                                 | 235 |

| H-5    | Intrinsic fixed charge and trapping properties of HfAlO interpoly dielectric layers  M. Bocquet ( Leti/ IMEP-CNRS ), G. Molas (Leti), H. Grampeix (Leti), J. Buckley (Leti), F. Martin (Leti),  J. P. Colonna (Leti), M. Gély (Leti), G. Pananakakis ( IMEP-CNRS ) , G. Ghibaudo ( IMEP-CNRS ),  B. De Salvo (Leti), S. Deleonibus (Leti)                                                                                                                              | 239 |

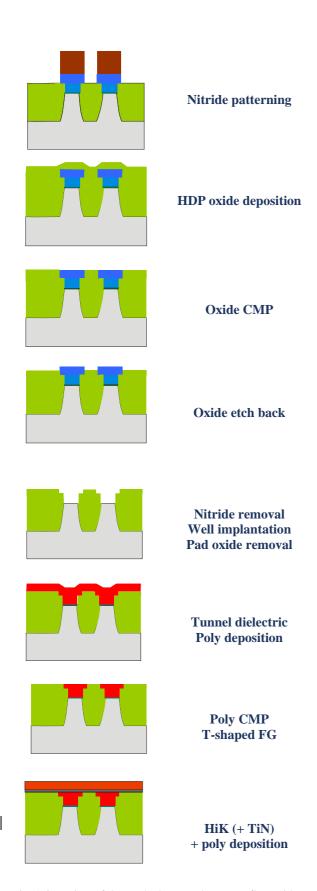

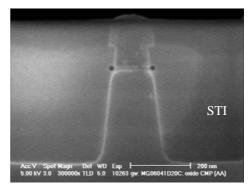

| Н-6    | A fully planar Stacked Gate Flash Technology with T-shaped Floating Gate for increased cell coupling ratio  J. De Vos, L. Haspeslagh, P. Blomme, M. Demand, K. Devriendt, F. Vleugels, D. Wellekens, J. Van Houdt (IMEC)                                                                                                                                                                                                                                               | 243 |

| H-7    | On the localization of the trapped charges in Silicon nanocrystal NOR Flash devices S. Jacob (Atmel/Leti), L. Perniola (Leti), B. De Salvo (Leti), E. Jalaguier (Leti), G. Festes (Atmel), R. Coppard (Atmel), F. Boulanger (Leti), S. Deleonibus (Leti)                                                                                                                                                                                                               | 247 |

| H-8    | Electrostatics and its effect on spatial distribution of tunnel current in metal Nanocrystal flash memories                                                                                                                                                                                                                                                                                                                                                            | 251 |

### **Memory Market Update: Shifting Dynamics**

Clare Hirst, Gartner Dataquest

It is clear that the immediate future of the memory market is centered on the fortunes of DRAM and flash memory technology.

It is not so clear how changing supply and demand dynamics will impact the market and how well the competing vendors are positioned for success.

And with new, emerging memory technologies constantly under development, there is always the possibility of even greater challenges ahead.

### **Charge-based versus Resistance-based Non-Volatile Memory**

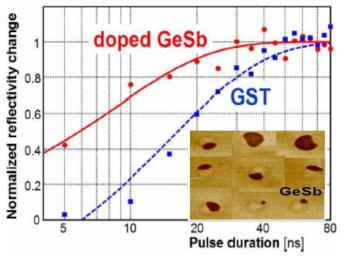

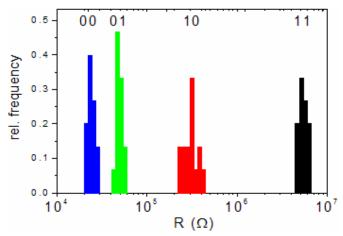

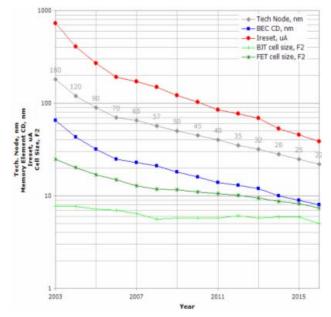

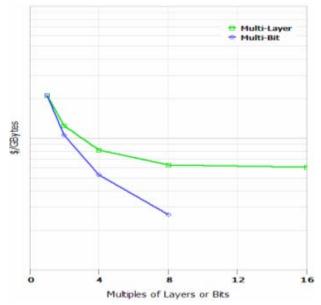

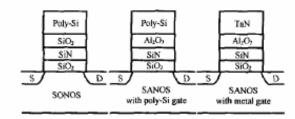

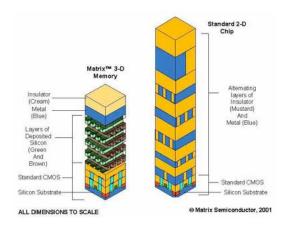

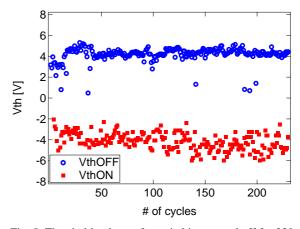

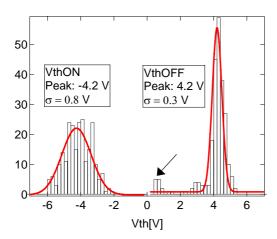

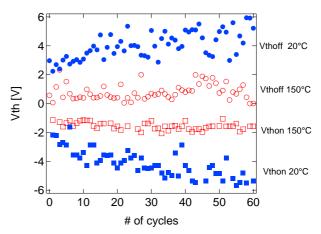

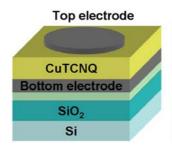

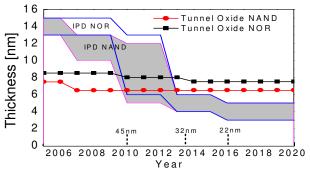

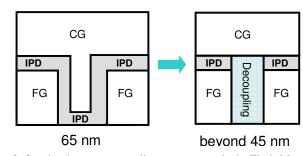

Flash, which is the standard Non-volatile Memory technology today, is based on the storage of charge in the floating gate of an MOS gate -stack, and by that controlling the transistor threshold voltage. However, further reduction of the charge (number of electrons) as needed for the further technology scaling may be limited by leakage current, while cell geometry reduction may induce important electrostatic effects. To cope with arising scaling issues, new alternative Flash concepts are proposed based on different charge storage media, as nanocrystals or silicon nitride.